# The Block Plan Problem

A Graphtheoretic Approach

U. J. NIEMINEN

A block plan graph is a planar one and the paper concentrates on the case of a block plan graph having perpendicular corners only. An algebraic criterion is defined for the planarity condition and the problem to find an optimal planar block plan graph is solved by integer linear programming.

#### 1. INTRODUCTION

The design of a block plan layout is a speciefied case of facility planning. A block plan is a diagrammatic representation of a facility showing internal partitions and allocation of area to various departments. In this paper we shall concentrate on the case, where the departments have perpendicular corners only. A block plan can be described as a planr graph, and in the restricted case of this paper the planarity of the graph can be expressed in the form of a set of linear equations. If the graph is non-planar, an optimal planar graph can be found by integer linear programming or by pseudo-boolean programming. In particular, the solution procedure of this paper is of interest to the design of a block plan layout in a single story building.

In the second section of this paper we shall recall a set of basic graphtheoretic concepts, and in the third we shall present the problem formulation. The fourth section contains a solution procedure, and in the fifth section an example and some remarks shall be given.

This paper is mainly based on the work [7] of Seppänen and Moore.

### 2. BASIC CONCEPTS

An unordered graph G, briefly graph G, is a pair (V(G), E(G)) of sets, where  $V(G) = \{x, y, z, ...\}$  is the set of vertices in G and E(G) the set of its edges. E(G) is a subset of the unordered pairs of vertices in V(G), denoted by (x, y),  $x, y \in V(G)$ .

A graph G has no loops if there are no edges from a vertex x to itself, and G has no multiple edges if (x, y) is the only edge connecting the vertices x and y in G. In the following we shall consider finite graphs without loops and multiple edges only.

A path in a graph G is defined as a sequence  $z_0, z_1, z_2, ..., z_p$  of vertices in V(G) so that  $(z_{i-1}, z_i) \in E(G)$  for every value of i, i = 1, ..., p. The length of the path is p. If  $z_0 = z_p$ , the path is called a circuit. Clearly a path and a circuit can be uniquely defined by their edges. A path is elementary, if it visits each of its vertices only once. A graph G is connected, if there is a path connecting any two vertices x and y of x0. A graph x1 is add to be nonseparable, if the removing of an edge or of a vertex from x2 does not disconnect x3.

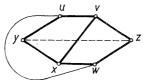

Fig. 1.

Every graph G is uniquely described by its associated  $n \times n$  matrix  $M = [m_{xy}]$ , called adjacency matrix, where  $m_{xy} = 1$ , if  $(x, y) \in E(G)$ , and  $m_{xy} = 0$  otherwise.

A graph is said to be planar, if it can be so mapped onto a plane that no two edges of it intersect. Figure 1 illustrates a planar graph. If an additional edge, like (y, z), were to be added, the graph would no longer have this property.

A face of a planar graph G is an area of the plane bounded by edges of the graph, and which contains neither edges nor vertices in its interior. The contour of a finite face is the circuit formed by the edges which surround it. Note that every planar graph has exactly one unbounded face, which is the infinite face.

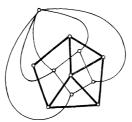

Fig. 2.

Consider a planar graph G having the faces  $\{f_s : s = 1, ..., q\}$ , with the infinite face included. Let us associate a point  $x_s$  within each face. We define the dual graph DG of G to be made up of these points as vertices and any two vertices being joined

by an edge whenever their corresponding faces in G are bounded by a common edge, i.e., if the faces are adjacent. Figure 2 illustrates this relationship with the planar graph G shown with heavy lines.

Let x be a vertex of a graph G. The incidence set of x in G, denoted by E(G, x), is the following

$$E(G, x) = \{(x, y) : y \in V(G)\}.$$

From a planar graph and its dual it can be directly verified that the number of edges in both graphs is the same, while the numbers of vertices and faces are interchanged. Also the number of edges contained by the contour of a face  $f_s$  in G is the number of edges in the incidence set  $V(DG, x_s)$ .

A graph is known to be planar if and only if it has a dual. An equivalent form to the statement above has been given by S. MacLane [6] and Lemma 1 below is a modification of his results (see e.g. Busacker and Saaty [3] and Dunn and Chan [4]).

**Lemma 1.** Given a nonseparable, unordered, connected graph G of n edges and m vertices having  $\mathscr C$  as the family of all its elementary circuits,  $\mathscr C = \{C_1, C_2, ..., C_t\}$ , where every  $C_i \in \mathscr C$  is expressed by the edges forming it. G is planar if and only if there is a graph G' so that the following conditions hold:

- (i) There is a one-to-one mapping between the edges of G and G'.

- (ii) There is a subfamily  $\mathscr{C}' \subset \mathscr{C}$  of n-m+2 circuits so that under the mapping h every circuit  $C_r \in \mathscr{C}$  corresponds to an incidence set  $V(G', x_r)$  and vice versa,  $r=1, \ldots, n-m+2$ .

Lemma 1 is a reformulation of Theorem 1 in [4]. Clearly G' in Lemma 1 is the dual of G. The solution procedure below is based on this lemma.

# 3. THE PROBLEM FORMULATION

We can consider a block plan (e.g. in Figure 3) as a graph as follows (Seppänen and Moore [7]). Each corner point in the plan, where at least three departments meet, is taken as a vertex of the graph. Note that the infinite face may appear as one of the three. The edges of a block plan graph are those pairs of vertices, which are connected by a wall. The corners, where only two departments meet, are not vertices. Defined in this manner, it can be seen that the block plan layout can be considered as a planar graph and the knowledge provided by graph theory can be applied.

The concept of duality defined as above is directly applicable to the design of a block plan layout. If G is the block plan graph, the dual DG can be thought of as representing the adjacency relationships among the departments as shown in Figure 4. Hence the graph DG is called a relationship diagram (Seppänen and Moore [7]).

Assume that a relationship diagram RD, or the corresponding adjacency matrix, defining all the departmental adjacency requirements of the block plan graph, is

given. A planar block plan graph G corresponding to the given RD exists if and only if RD is planar. Besides, RD = DG. Unfortunately, often in practical problems the graph RD is nonplanar and hence no block plan graph, which would satisfy all the desired adjacencies, exists. It implies that some of the desired adjacencies must be abandoned in order to obtain a planar block plan graph.

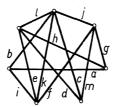

Fig. 3.

Let X be such a set of edges in RD, deletion of which makes RD planar. Following Seppänen and Moore we call X a resolving set. A resolving set X is minimal, if any of its proper subset does not have this property. A minimal resolving set X is a minimum resolving set, if there is no resolving set X' in RD having a fewer number of

Fig. 4.

edges than X. For every resolving set  $X_i$  of RD, the graph  $RD_i = (V(RD), E(RD) - X_i)$  is planar and determines thus a solution to the block plan layout design problem. In the following we consider a way to determine the minimum resolving set X of RD in the case, where the departments of the block plan graph have perpendicular corners.

If the departments in the block plan graph G have perpendicular corners only, i.e.  $V(G, x_s)$  contains at most four edges for every  $x_s \in V(G)$ , the contours of the faces in DG contain at most four edges. According to the definition of a block plan graph G, for every  $x_s \in V(G)$   $V(G, x_s)$  contains at least three edges. Hence the family  $\mathscr{F}$  of the faces of DG is contained by the family  $\mathscr{C}_3 \cup \mathscr{C}_4$  of all the elementary circuits of length three and four in DG. In the following we construct a systematic way to find the family  $\mathscr{F}$  of faces among the circuits of the family  $\mathscr{C}_3 \cup \mathscr{C}_4$ . The method presented here is a slight modification of that proposed by Dunn and Chan in their paper [4].

In what follows we assume that the graph RD is nonseparable. The assumption is realistic, as we shall below show, and necessary for the application of Lemma 1.

Let the number of edges in E(RD) be n and let a family  $\mathscr{V}_{34}$  contain all vectors  $V_r = (u_{r1}, u_{r2}, u_{r3}, ..., u_{rn})$  each of which represents a circuit of the family  $\mathscr{C}_3 \cup \mathscr{C}_4$  of RD, r = 1, ..., k. Every  $C_r \in \mathscr{C}_3 \cup \mathscr{C}_4$  is expressed by its edges. In  $V_r$ ,  $u_{rj} = 1$ , if the edge corresponding to index j belongs to the circuit represented by  $V_r$ , in other cases  $u_{rj} = 0$ .

One edge of a graph without loops joins exactly two vertices. This trivial observation and Lemma 1 give the following criteria for the planarity of a graph RD. A graph RD is planar and  $\mathscr{F} \subset \mathscr{C}_3 \cup \mathscr{C}_4$  if and only if there is a set of coefficients  $a_1, a_2, a_3, \ldots, a_k, a_r = 0, 1$  so that the vector sum of the vectors  $a_r V_r, V_r \in \mathscr{V}_{34}$ , is a vector containing only twos, i.e.

(1)

$$\sum_{r=1}^{r=k} a_r V_r = \sum_{r=1}^{r=k} a_r (u_{r1}, u_{r2}, ..., u_{rn}) = (2, 2, ..., 2).$$

If (1) is valid, then clearly all the circuits  $C_{r_2}, C_{r_3}, ..., C_{r_q} \in \mathscr{C}_3 \cup \mathscr{C}_4$  for which the coefficients  $a_{r_1}, a_{r_2}, ..., a_{r_q}$  have the value 1 in (1) are the circuits of subfamily  $\mathscr{C}'$  in Lemma 1

(1) can be expressed in an other but equivalent form

(2)

$$a_{1}u_{11} + a_{2}u_{21} + a_{3}u_{31} + \dots + a_{k}u_{k1} = 2,$$

$$u_{1}u_{12} + a_{2}u_{22} + a_{3}u_{32} + \dots + a_{k}u_{k2} = 2,$$

$$\vdots \qquad \vdots \qquad \vdots \qquad \vdots \qquad \vdots$$

$$a_{1}u_{1n} + a_{2}u_{2n} + a_{3}u_{3n} + \dots + a_{k}u_{kn} = 2,$$

giving the base to find a minimum resolving set in the case of a nonplanar RD.

If RD is nonplanar and if an edge j belongs to a resolving set, then the removing of j from RD implies that all the circuits of  $\mathscr{C}_3 \cup \mathscr{C}_4$  containing edge j must be abandoned. This will happen by putting the sum corresponding to j in (2) equal to zero, i.e.  $a_1u_{1j} + a_2u_{2j} + a_3u_{3j} + \ldots + a_ku_{kj} = 0$ . If simultaneously the other sums in (2) equals to two, the graph (V(RD), E(RD) - j) is planar and  $\mathscr{F} \subset \mathscr{C}_3 \cup \mathscr{C}_4$ . The operations above can be performed systematically, if we choose n new variables

$b_1, b_2, ..., b_n$ , and write the calculation scheme into the form of a linear programming scheme. We obtain the following scheme:

maximize

(3)

$$c_1b_1 + c_2b_2 + c_3b_3 + \ldots + c_nb_n$$

with subject to

(4)

$$a_1u_{11} + a_2u_{21} + \dots + a_ku_{k1} - 2b_1 = 0,$$

$$a_1u_{12} + a_2u_{22} + \dots + a_ku_{k2} - 2b_2 = 0,$$

$$\vdots \qquad \vdots \qquad \vdots \qquad \vdots \qquad \vdots$$

$$a_1u_{1n} + a_2u_{2n} + \dots + a_ku_{kn} - 2b_n = 0,$$

and

(5)

$$a_r = 0, 1, \quad r = 1, ..., k, \\ b_p = 0, 1, \quad p = 1, ..., n.$$

If an edge j belongs to the resolving set given by the scheme above, the corresponding variable  $b_j$  has the value 0, whence  $a_1u_{1j} + a_2u_{2j} + a_3u_{3j} + \ldots + a_ku_{kj} = 0$  as presupposed above.

The non-negative numbers  $c_1, c_2, c_3, \ldots, c_n$  are assigned to the edges according to the relative intensity of interrelations between two departments in the plan. If the values of the coefficients  $c_1, c_2, \ldots, c_n$  are chosen so that the value of every sum of m coefficients is less than the value of any sum of m+1 coefficients, the variables  $b_{j_1} = b_{j_2} = b_{j_3} = \ldots = b_{j_t} = 0$  given by the scheme above define a minimum resolving set  $X = \{j_1, j_2, j_3, \ldots, j_t\}$ .

Clearly the graph RD can be so constructed that it is nonseparable. If the removing of an edge j from RD would produce a separating edge, say g, g necessarily belongs merely to the elementary circuits of length three and four containing j. Hence the removing of j always implies removing of g and the two disjoint subgraphs thus obtained do not contain any separating edges. If a graph (V(RD), E(RD) - Z), where Z is a set of edges, contains a separating vertex y, the scheme described by (3), (4), and (5) considers it as two disjoint graphs, and hence y does not imply any consults on.

It is worth noting that the removing of an edge j from RD produces no new circuits of length three and four. Hence the scheme of (3), (4), and (5) determines a family  $\mathscr{F}$  of faces,  $\mathscr{F} \subset \mathscr{C}_3 \cup \mathscr{C}_4$ , if such exists.

## 5. AN EXAMPLE AND SOME REMARKS

Consider the graph RD in Figure 5 (Seppänen and Moore). The following elementary circuits of length three and four expressed by their edges can be found:

$$\mathscr{C}_3 = \{C_1 = \{b, i, k\}, C_2 = \{e, k, l\}, C_3 = \{f, j, k\}, C_4 = \{c, d, l\}, C_5 = \{c, j, m\}\},\$$

$$\mathcal{C}_{4} = \left\{ C_{6} = \left\{ a, f, g, i \right\}, \ C_{7} = \left\{ a, b, g, j \right\}, \ C_{8} = \left\{ a, b, h, l \right\}, \ C_{9} = \left\{ a, e, h, i \right\}, \\ C_{10} = \left\{ b, e, i, l \right\}, \ C_{11} = \left\{ b, f, i, j \right\}, \ C_{12} = \left\{ c, d, e, k \right\}, \ C_{13} = \left\{ j, g, h, l \right\}, \\ C_{14} = \left\{ e, f, j, l \right\}, \ C_{15} = \left\{ d, e, f, m \right\}, \ C_{16} = \left\{ c, f, k, m \right\}, \ C_{17} = \left\{ d, g, h, m \right\}, \\ C_{18} = \left\{ d, j, l, m \right\}, \ C_{19} = \left\{ e, f, g, h \right\} \right\}.$$

371

Fig. 5.

The vectors of family  $\mathscr{V}_{34}$  representing the elementary circuits of  $\mathscr{C}_3 \cup \mathscr{C}_4$  have been collected to the following matrix:

(6) abcdefghijklm $V_1$ 0 1 0 0 0 0 0 0 1 0 1 0 0  $V_{2}$  $V_3$  $V_4$  $V_5$   $V_6$   $V_7$  $V_8$  $V_9$  $V_{10}$  $V_{11}$  $V_{12}$  $V_{13}$  $V_{14}$ 0 0 0 0  $V_{15}$ 0 0 0 0 1 0 0 1 0 0 1  $V_{16}$  $V_{17} | 0 0 0$ 1 0 0 1  $V_{18} \ | \ 0 \ 0 \ 0 \ 1 \ 0 \ 0 \ 0 \ 0 \ 1 \ 0 \ 1$

$1 \quad 2 \quad 3 \quad 4 \quad 5 \quad 6 \quad 7 \quad 8 \quad 9 \ 10 \ 11 \ 12 \ 13$

By a calculation or by the method given by Dunn and Chan in [4] one can see that there is no family  $\mathscr{F}, \mathscr{F} \subset \mathscr{C}_3 \cup \mathscr{C}_4$ , and hence RD is nonplanar. According to (3), (4), and (5), we obtain the following linear programming scheme, where  $c_1 = c_2 = \ldots = c_{13} = 1$ . In the scheme the equations in (4') correspond to the columns of matrix (6):

(3')  $b_1 + b_2 + b_3 + b_4 + b_5 + b_6 + b_7 + b_8 + b_9 + b_{10} + b_{11} + b_{12} + b_{13}$  with subject to

(4')

$$a_{6} + a_{7} + a_{8} + a_{9} - 2b_{1} = 0,$$

$$a_{1} + a_{7} + a_{8} + a_{10} + a_{11} - 2b_{2} = 0,$$

$$a_{4} + a_{5} + a_{12} + a_{16} - 2b_{3} = 0,$$

$$a_{4} + a_{12} + a_{15} + a_{17} + a_{18} - 2b_{4} = 0,$$

$$a_{2} + a_{9} + a_{10} + a_{12} + a_{14} + a_{15} + a_{19} - 2b_{5} = 0,$$

$$a_{3} + a_{6} + a_{11} + a_{14} + a_{15} + a_{16} + a_{19} - 2b_{6} = 0,$$

$$a_{6} + a_{7} + a_{13} + a_{17} + a_{19} - 2b_{7} = 0,$$

$$a_{8} + a_{9} + a_{13} + a_{17} + a_{19} - 2b_{8} = 0,$$

$$a_{1} + a_{6} + a_{9} + a_{10} + a_{11} - 2b_{9} = 0,$$

$$a_{3} + a_{5} + a_{7} + a_{11} + a_{13} + a_{14} + a_{18} - 2b_{10} = 0,$$

$$a_{1} + a_{2} + a_{3} + a_{12} + a_{16} - 2b_{11} = 0,$$

$$a_{2} + a_{4} + a_{8} + a_{10} + a_{13} + a_{14} + a_{18} - 2b_{12} = 0,$$

$$a_{5} + a_{15} + a_{16} + a_{17} + a_{18} - 2b_{13} = 0,$$

and

(5')

$$a_r = 0, 1, \quad r = 1, 2, ..., 19,$$

$b_p = 0, 1, \quad p = 1, 2, ..., 13.$

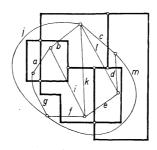

Fig. 6.

A calculation shows that, if  $b_8=0$ , then the values  $a_1=a_2=a_4=a_5=a_6=a_7=1_5=1$ ,  $a_3=a_8=a_9=a_{10}=a_{11}=a_{12}=a_{13}=a_{14}=a_{16}=a_{17}=a_{18}=a_{19}=0$ ,  $b_1=b_2=b_3=b_4=b_5=b_6=b_7=b_9=b_{10}=b_{11}=b_{12}=b_{13}=1$  satisfy (4') and (5'), and hence  $X=\{h\}$  is a minimum resolving set. The corresponding graph RD'=(V(RD),E(RD)-h) and its dual are given in Figure 6.

The method to solve a block plan design problem presented here needs an efficient method to enumerate all the elementary circuits of length three and four in RD. It is very difficult to say, if there exists any efficient method, but we would recommend the Latin multiplication (see e.g. [5], pp. 188-192) and the methods proposed by C. Benzaken in his papers [1] and [2]. As pointed out by Dunn and Chan in [4], the way proposed here can be applied to the case where  $\mathscr{F} \subset \mathscr{C}_3 \cup \mathscr{C}_4 \cup \ldots \cup \mathscr{C}_{m-1}$  as well, but then the constraint set (4) may have an unpractical large number of variables  $a_r$ .

Finally we list some rather good properties of the method considered above:

- The planarity test can be expressed in the form of a set of linear equations.

- A minimum resolving set can be determined.

- The method allows to use unequal weights  $c_1, c_2, ..., c_n$ .

- The final block plan graph can directly be drawn by the incidence sets defined by the variables  $a_{r_1} = a_{r^2} = a_{r_2} = \dots = a_{r_n} = 1$ .

(Received February 9, 1973.)

#### REFERENCES

- C. Benzaken: Pseudo-treillis distributifs et applications III. Buletinul Institutului Politehnic din Iasi XIV (1968), 3-4, 25.

- [2] C. Benzaken: Structures algébriques des cheminements: Pseudo-treillis, gerbiers carré nul. In: "Network and switching theory. A NATO advanced study institute" ed. by G. Biorci, 1968, p. 40.

- [3] R. Busacker, T. Saaty: Finite graphs and networks: An Introduction with applications. McGraw-Hill, New York 1965.

- [4] W. R. Dunn Jr., S. P. Chan: An algorithm for testing the planarity of a graph. IEEE Transactions on Circuit Theory CT-15 (1968), 166.

- [5] P. L. Hammer, S. Rudeanu: Boolean methods in operations research and related areas. Springer-Verlag, Berlin-Heidelberg 1968.

- [6] S. MacLane: A combinatorial condition for planar graphs. Fundamenta Mathematica 28 (1937), 22.

- [7] J. J. Seppänen, J. M. Moore: Facilities planning with graph theory. Management Science (Application) 17 (1970), B-242.

Juhani Nieminen, Research assistant, Finnish Academy, Department of technical sciences, Helsinki, Finland.